# INDIAN INSTITUTE OF TECHNOLOGY, GANDHINAGAR

#### MASTERS THESIS

# Accelerating Large Integer Arithmetic with Parallel Addition, Subtraction, and Vedic-Based Multiplication Using AVX512

# by **Subhrajit DAS**

A thesis submitted in partial fulfilment of the requirements for the degree of **Master of Technology**

in

Computer Science and Engineering

April, 2025

## Abstract

Large operands exceeding the standard 32- or 64-bit register sizes of most modern CPUs are common in cryptography, scientific computing and other allied areas. Arithmetic operations like addition, subtraction, multiplication, division, modulo, and factorization are essential in this context. Scientific computing typically employs commercial tools like Maxima or Mathematica, while cryptography relies on optimized libraries such as GNU Multiple Precision Library (GMP) and BigInt. However, despite their fine-tuned optimizations for most general-purpose processors, they underutilize modern CPU parallelization capabilities like SIMD (Single Instruction, Multiple Data), possibly due to limited research on parallelizing core arithmetic tasks.

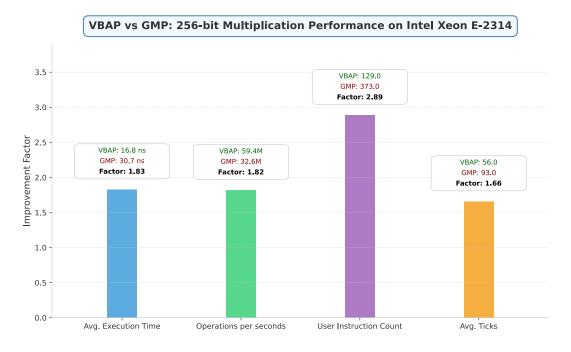

In this work, we address this gap by focusing on three fundamental operations: addition, subtraction, and multiplication of large integers. We propose a parallel approach for the addition and subtraction of these integers. Additionally, we introduce a hybrid multiplication technique that incorporates the ancient Indian Vedic mathematics, Urdhva-Tiryagbhyam sutra, which is traditionally aimed at faster mental multiplication. Using SIMD constructs, particularly the AVX512 intrinsics on an x86-64 Intel Rocket Lake-based CPU, we achieve an average execution time speed-up of 2.06x for addition and 2.32x for subtraction in 99.99% of cases compared to GMP on operand sizes ranging between 256 bits and 131072 bits. Even in the worst-case scenarios, our performance remains competitive with GMP, resulting in an average speed-up of 1.38x for addition and 1.49x for subtraction. Furthermore, compared to GMP, we outperformed the existing works for large number addition and subtraction on x86-64-based CPUs. However, our implementation of the multiplication algorithm using the Vedic approach currently supports only fixed 256-bit-sized operands, achieving a performance gain of 1.83 times in execution time over GMP. Notably, none of the existing works utilizing the AVX512 intrinsics have been able to outperform GMP for multiplications involving fewer than 1024-bit operands. Future research will focus on completing the hybrid multiplication implementation for variable-sized operands and fine-tuning the implementations for other architectures, such as ARM and RISC-V, using their respective SIMD constructs.

# Acknowledgements

With a whole heart, I sincerely want to thank my advisor and my guide, **Abhishek Bichhawat**, who has been very supportive throughout the entire duration of my M.Tech thesis. Apart from research, I learned from him how a good professor, a good advisor, and, foremost, a good human should be. Additionally, I want to sincerely thank my co-advisor, **Yuvraj Patel**, an excellent researcher, who actively engaged with my evolving ideas and offered thoughtful perspectives throughout this thesis. I appreciate his observations and ideas, which I most often overlooked during the course of this work. Both of my advisors have been incredibly supportive and approachable, guiding me through the highs and lows of my research journey.

I also extend my thanks to the Department of Computer Science and Engineering at the Indian Institute of Technology Gandhinagar for providing me access to essential laboratory resources. Additionally, for more than half of the thesis timeline, I ran my initial experiments on CloudLab [Dup+19] CPUs, and I am truly grateful to Yuvraj Sir for providing me access to such a helpful platform. In the latter half, I switched to working with a newer CPU at the Institute, procured by Abhishek Sir. This CPU was extremely helpful as it had the necessary features that I needed.

I am deeply grateful to **my family, friends, and teachers** for their unwavering love, support, and faith. I also cherish the memory of all **my beloved pets** for the unique love and comfort they brought into my life. Without them all, I wouldn't have been able to reach this phase of my life and achieve many of my dreams. Whatever I am now is because of them.

# **Contents**

| <b>A</b> l | bstrac | ct                                                     | i   |

|------------|--------|--------------------------------------------------------|-----|

| A          | cknov  | wledgements                                            | ii  |

| Li         | st of  | Figures                                                | vi  |

| Li         | st of  | Tables                                                 | vii |

| Li         | st of  | Abbreviations                                          | i   |

| 1          |        | oduction                                               | 1   |

|            | 1.1    | Problem Statement                                      | 2   |

|            |        | 1.1.1 Optimizing Arithmetic Operations                 | 2   |

| 2          |        | kground & Related Works                                | 4   |

|            | 2.1    | Large Numbers                                          | 4   |

|            |        | 2.1.1 Large Number Representation                      | 4   |

|            | 2.2    | Addition                                               | 5   |

|            |        | 2.2.1 Carry Propagate Addition                         | 5   |

|            |        | 2.2.2 Carry Select Addition                            | 6   |

|            | 2.3    | Subtraction                                            | 7   |

|            | 2.4    | Multiplication                                         | 8   |

|            |        | 2.4.1 Grade-school                                     | 8   |

|            |        | 2.4.2 Divide-and-Conquer Multiplication Strategies     | ç   |

|            |        | Karatsuba                                              | ç   |

|            |        | Toom-Cook                                              | 10  |

|            |        | 2.4.3 Fast Fourier Transformation                      | 11  |

|            | 2.5    | Vedic Mathematics                                      | 11  |

|            |        | 2.5.1 Urdhva-Tiryagbhyam Sutra for Multiplication      | 13  |

|            | 2.6    | Related Works on Parallel Arithmetic for Large Numbers | 17  |

|            |        | 2.6.1 Addition and Subtraction                         | 17  |

|            |        | 2.6.2 Multiplication                                   | 20  |

|            | 2.7    | Vectorization (SIMD)                                   | 22  |

|            |        | 2.7.1 AVX-512                                          |     |

|            |        | 2.7.2 AVX-10                                           |     |

|            | 2.8    | Parallel Algorithm Design                              |     |

| 3          | Para   | allelizing the Addition of Large Integers              | 26  |

|            | 3.1    | Parallel Multi-phase Addition Algorithm                | 26  |

|            |        | 3.1.1 Proposed Addition Algorithm                      |     |

|            | 3.2    | Implementation of Proposed PML Add using AVX-512       |     |

|            |        | 3.2.1 Data Representation                              | 29  |

|            |        | 3.2.2 Implementations                                  |     |

|            |        | Sub-optimal Implementations                            |     |

|      |       | Final Implementation of PML Add                                | 32 |

|------|-------|----------------------------------------------------------------|----|

|      | 3.3   | Evaluation                                                     | 36 |

|      |       | 3.3.1 Correctness                                              |    |

|      |       | 3.3.2 Performance Compared to GMP and Baseline                 |    |

| 4    | Para  | Illelizing the Subtraction of Large Integers                   | 41 |

|      | 4.1   | Parallel Multi-phase Subtraction Algorithm                     | 41 |

|      |       | 4.1.1 Proposed Subtraction Algorithm                           |    |

|      | 4.2   | Implementation of Proposed PML Sub using AVX-512               | 41 |

|      | 4.3   | Evaluation                                                     | 44 |

|      |       | 4.3.1 Correctness                                              | 44 |

|      |       | 4.3.2 Performance Compared to GMP and Baseline                 |    |

| 5    | App   | roximate Parallel Addition and Subtraction for Large Integers  | 46 |

|      | 5.1   | Chained Carry Propagation                                      | 46 |

|      |       | 5.1.1 Likelihood of Chained Carry Propagation                  |    |

|      | 5.2   | Parallel Multi-phase Approximate Addition                      | 50 |

|      | 5.3   | Parallel Multi-phase Approximate Subtraction                   |    |

|      | 5.4   | Evaluation                                                     | 52 |

|      | 0.1   | 5.4.1 Correctness                                              |    |

|      |       | 5.4.2 Performance Compared to GMP and PML Add                  | 53 |

| 6    | Acce  | elerating the Multiplication of Large Integers                 | 57 |

| U    | 6.1   | Parallel Hybrid-Multiplication                                 |    |

|      | 0.1   | •                                                              | 58 |

|      |       |                                                                | 60 |

|      |       | J 11                                                           |    |

|      | ( )   | Proposed Hybrid Algorithm                                      | 61 |

|      | 6.2   | Implementation of Proposed 256-bit VBAP Mul using AVX512-IFMA. | 61 |

|      |       | 6.2.1 Data Representation                                      | 61 |

|      |       | 6.2.2 Sub-optimal Implementations                              |    |

|      |       | Final Implementation using AVX512-IFMA                         |    |

|      | 6.3   | Evaluation                                                     |    |

|      |       | 6.3.1 Correctness                                              |    |

|      |       | 6.3.2 Performance Compared to GMP                              | 73 |

| 7    | Disc  | cussion and Limitations                                        | 74 |

|      | 7.1   | Discussion                                                     | 74 |

|      | 7.2   | Limitations                                                    | 77 |

| 8    | Con   | clusion and Future Scope                                       | 79 |

| Bi   | bliog | raphy                                                          | 81 |

| Δ    | Mea   | surement Techniques                                            | 88 |

| 4 \$ |       | Timing Measurements                                            | 88 |

|      | 11.1  | A.1.1 RUSAGE                                                   | 88 |

|      |       | A.1.2 RDTSC                                                    | 88 |

|      |       |                                                                |    |

|      |       | A.1.3 Timespec                                                 | 89 |

|      | 4 0   | A.1.4 Measuring Execution Time and Number of Operations        | 90 |

|      | A.2   | Code Profiling                                                 | 91 |

|      |       | A.2.1 PERF                                                     | 91 |

| В | Mis        | cellaneous Optimization Techniques          | 92 |

|---|------------|---------------------------------------------|----|

|   | B.1        | Auto-Vectorization                          | 92 |

|   | B.2        | Aligned Memory Allocation for Vectorization | 92 |

|   | B.3        | Transparent Huge Pages (THP)                | 92 |

|   | <b>B.4</b> | Branching Optimization                      | 93 |

# **List of Figures**

| 2.1        | Urdhva-Tiryagbhyam Multiplications (set-wise) [Upa]                                                                          | 14   |

|------------|------------------------------------------------------------------------------------------------------------------------------|------|

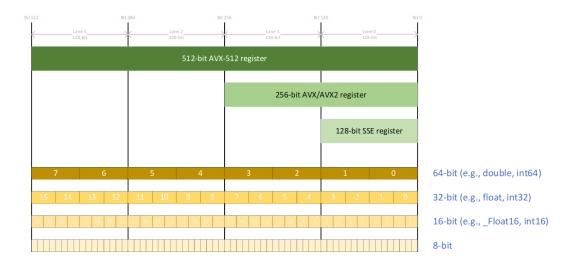

| 2.2        | Layout of Various Sizes of SIMD Register and How Each Can Be Bro-                                                            |      |

|            | ken Down into Smaller Subgroups of Elements [Tow22]                                                                          | 24   |

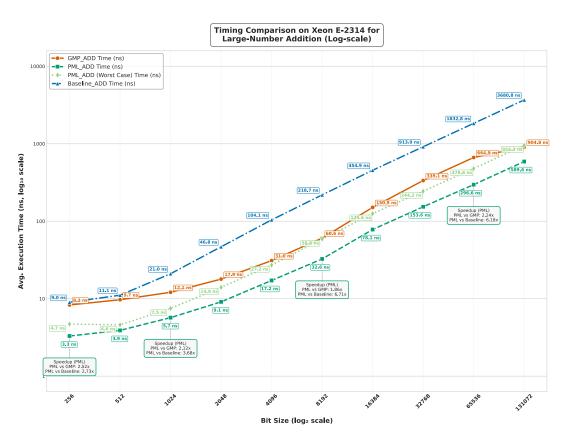

| 3.1<br>3.2 | Overview of AVX Lane operations for eight limbs using PML ADD Timing comparison of PML Add, PML Add Worst, Baseline Add, and | 36   |

|            | GMP Add for various data sizes on Intel Xeon E-2314                                                                          | 40   |

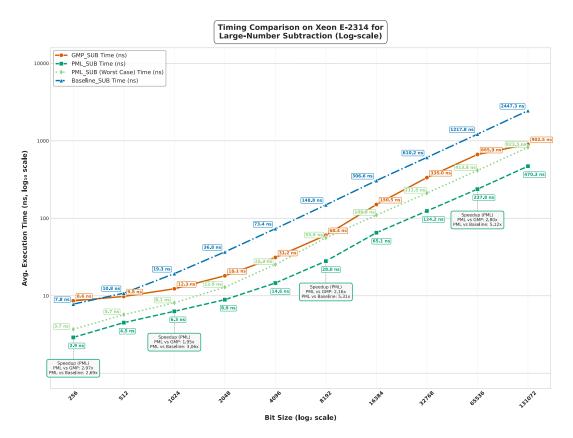

| 4.1        | Timing comparison of PML Sub with GMP Sub for various data sizes                                                             |      |

|            | on Intel Xeon E-2314                                                                                                         | 45   |

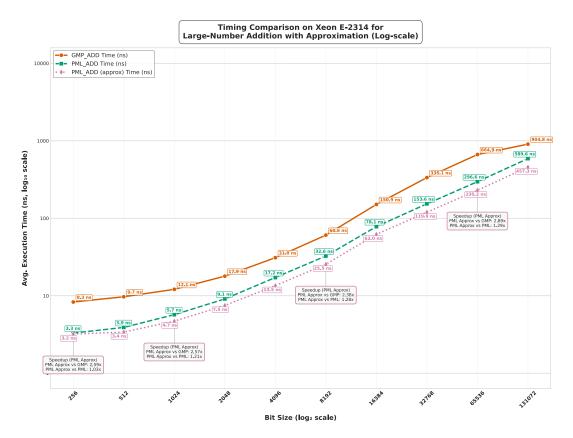

| 5.1        | Timing comparison of PML Add (Approx) with GMP and PML Add                                                                   |      |

|            | for various data sizes on Intel Xeon E-2314                                                                                  | 53   |

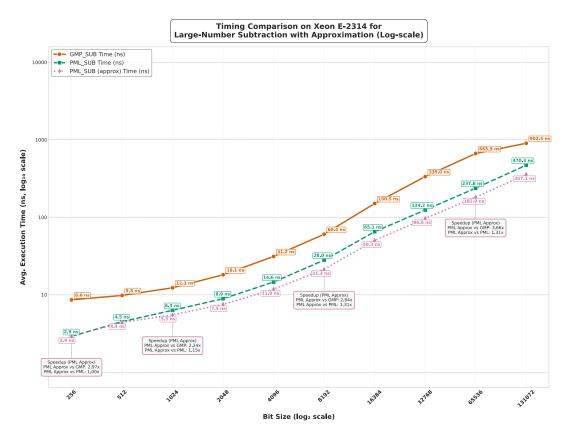

| 5.2        | Timing comparison of PML Sub (Approx) with GMP and PML Sub                                                                   |      |

|            | for various data sizes on Intel Xeon E-2314                                                                                  | 54   |

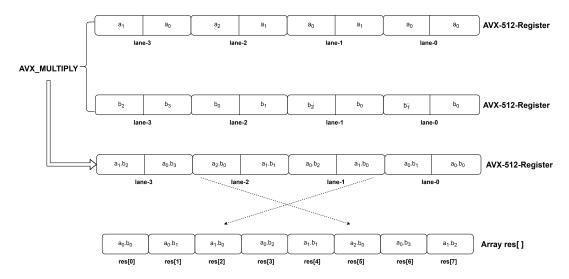

| 6.1        | Example of AVX Lanes containing the operands while multiplying                                                               |      |

|            | and storing (Group-1)                                                                                                        |      |

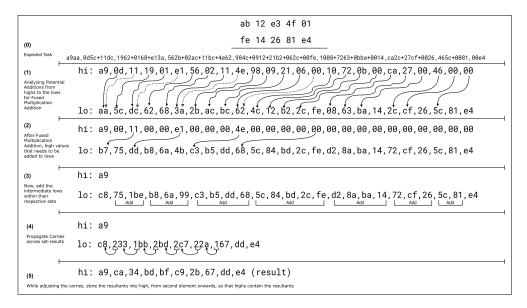

| 6.2        | Example of Proposed Urdhva-Tiryagbhyam Five-Limb Fused-Multiplica                                                            | tion |

|            | Addition Technique                                                                                                           | 69   |

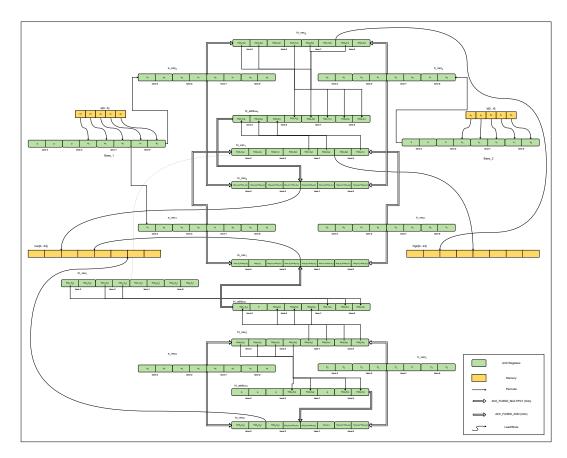

| 6.3        | Overview of AVX Lane operations for five limb VBAP MUL using IFMA                                                            | 72   |

| 6.4        | VBAP vs. GMP: Performance Gains on Intel Xeon E-2314 (256-bit Mul)                                                           | 73   |

# **List of Tables**

| 2.1 | Summary of the Sixteen Vedic Sutras                                                                                         | 12        |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----------|

| 2.2 | Operation counts for grade-school and Urdhva-Tiryagbhyam multiplication of two <i>n</i> -digit numbers                      | 17        |

| 2.3 | Evolution of SIMD Instruction Sets Across Major CPU Vendors                                                                 | 23        |

| 5.1 | Summarized Execution Time Statistics of Addition by Operand Size Across Models (in ns)                                      | 54        |

| 5.2 | Summarized Ticks Statistics of Addition by Operand Size Across Models                                                       | 55        |

| 5.3 | Summarized Throughput Statistics of Addition by Operand Size Across Models (in million OP/s)                                | 55        |

| 5.4 | Summarized User Instructions Statistics of Addition by Operand Size Across Models                                           | 55        |

| 5.5 | Summarized Execution Time Statistics of Subtraction by Operand Size Across Models (in ns)                                   | 55        |

| 5.6 | Summarized Throughput Statistics of Subtraction by Operand Size Across Models (in million OP/s)                             | 56        |

| 5.7 | Summarized Ticks Statistics of Subtraction by Operand Size Across                                                           |           |

| 5.8 | Models                                                                                                                      | 56        |

|     | Size Across Models                                                                                                          | 56        |

| 6.1 | Asymptotic Comparison of Number of Multiplications                                                                          | 57        |

| 6.2 | Timing (in $\mu$ s) comparison VBAP_MUL (64-bit Limbs, split-into 32-bit sub-limbs, AVX512-F) with GMP on Intel Xeon E-2314 | 64        |

| 6.3 | Timing(in $\mu$ s) of different utility functions for VBAP_MUL(64-32,AVX512 on Intel Xeon E-2314                            | 2F)<br>64 |

| 6.4 | High-Low Index Mapping for five limbs IFMA AVX Multiplication for Basecase 256-bit VBAP MUL                                 | 69        |

# **List of Abbreviations**

PML Add Parallel Multi-Stage Large-Number Addition

PML Sub Parallel Multi-Stage Large-Number Subraction

VBAP Mul Vedic-based Approach for Multiplication

SIMD Single Instruction, Multiple Data AVX Advanced Vector Extensions

**GMP** GNU Multiple Precision Arithmetic Library

To my love and passion towards computer science...

### Chapter 1

## Introduction

Large-number arithmetic, also known as arbitrary-precision or BigNum arithmetic, plays a fundamental role in the current context of cryptography [Hel79; RSA78; Mil86; JMV01; Fre10; Erb+20], scientific computing [Bai05; BB15; BBB12], and various mathematical software packages [Sag; Wol; Max; Inc22]. RSA encryption [RSA78], for example, depends on the difficulty of factoring large primes for its security. Blockchain technologies, such as Bitcoin and Ethereum, use elliptic curve cryptography [Mil86] for securing transactions operating on large numbers. Scientific computing, including fields like astrophysics and particle physics [BB15], utilizes arbitraryprecision arithmetic for calculations. These large-number or arbitrary-precision arithmetic fundamentally require operations like addition, subtraction, multiplication, division and factorization on numbers [Ski08; Knu97] spanning hundreds and thousands of bits. However, working with large operands can significantly slow down the overall performance of applications. For example, the performance of RSA encryption varies exponentially with key size. Decrypting a 2048-bit RSA key takes only a few milliseconds; however, when the key size is doubled to 4096 bits, the time required can increase nearly fivefold on modern CPUs like the Intel i7 and Apple M1 [Cof]; additionally, generating key pairs can take almost ten times longer. And as the size of the operands increases, the computation time grows exponentially.

Current solutions for performing large-number arithmetic include commercial computer algebra systems like Maxima [Max] and Mathematica [Wol], as well as various libraries such as the GNU Multiple Precision Arithmetic Library (GMP) [GNU91] and the GNU Multiple Precision Floating-Point Reliable library (MPFR) [Pro] (based on GMP) in C/C++; gmpy2 [PYP] (based on GMP), mpmath [Joh], and the built-in decimal module in Python; the built-in BigInteger [Docb] in Java; Apfloat [Tom] in C++ and Java; the BigInt [Doca] in JavaScript; num-bigint [Docc] and rug [Docd] (based on GMP and MPFR) in Rust; and various other libraries.

The GMP library [GNU91] is widely used for fast arithmetic computations on large numbers and is highly optimized for most general-purpose processors, leveraging carefully tuned assembly routines. As a result, it serves as the foundation for many other libraries supporting large-number and arbitrary precision arithmetic. However, despite its optimizations, GMP is primarily designed for single-threaded sequential execution and does not take into account modern hardware capabilities for parallel computation, possibly due to limited work in parallelizing the large-number arithmetic operations. We believe that incorporating parallel algorithms with current hardware enhancements can significantly boost the performance.

Earlier works [Coo00; GK12; KM14; GK16] have tried to introduce parallelism in large number multiplication to enhance performance, focusing on metrics like instruction count and CPU cycles. However, the actual performance improvements in terms of execution time on modern hardware remain unclear, primarily due to the

absence of upgraded SIMD features in the commercial CPUs available at that time. Though some recent works [ET18; ET20; ET23] have introduced parallelism in this context, testing on some recent real-time actual CPUs and measuring in terms of execution time, they got performance improvements above 1024- to 3072-bit operand sizes against the current optimized single-threaded implementation of GMP. On the other hand, there's very limited work done [Yee19; RSS23] on accelerating largenumber addition and subtraction, but hardly getting significant performance improvements as with multiplication. Parallelism in computing can be broadly categorized into two types: Task-level Parallelism and Data-level Parallelism [HP11]. Task-level parallelism can be achieved using multi-threading, where independent tasks or operations are executed concurrently across multiple CPU cores. This approach can be beneficial for accelerating computation, but it also introduces bottlenecks due to complex thread management and synchronization overhead [Lee06; Asa+06; Pau]. Multi-threading is generally useful only beyond a certain data threshold, as thread overhead can degrade performance instead of improving it; thus, a few existing works [Sam22] noticed performance benefits only for abruptly large integers (ranging between  $6.4 \times 10^6$  to  $6.4 \times 10^{10}$  bits). Data-level parallelism, on the other hand, can be exploited using Single Instruction Multiple Data (SIMD) constructs on modern CPUs, where multiple data elements are processed simultaneously within a single instruction cycle. SIMD-based methods can achieve significant performance improvements, especially with larger vector register sizes (typically 256 bits and above), when used with parallel algorithms. However, suitable parallel algorithms have not been explored extensively for large-number arithmetic.

#### 1.1 Problem Statement

Our focus in this work is to design, implement and optimize algorithms for largenumber arithmetic using data-level parallelism, specifically through the use of SIMD constructs with x86-64 AVX512 intrinsics [Int24]. We target three fundamental arithmetic operations on large integers: addition, subtraction and multiplication.

More formally,

**Input description:** Given two large integers, *x* and *y*,

**Problem description:** Design high-performance AVX512-based parallel methods to compute x + y, x - y, and  $x \times y$ , minimizing each operation's computation time.

Further, we would like to compare the performance of these implementations against the widely used GMP library to assess improvements in execution speed, as GMP leverages highly optimized single-threaded assembly routines for addition, subtraction and multiplication and has not currently utilized SIMD for them [SIM].

#### 1.1.1 Optimizing Arithmetic Operations

To address the problem statement, we have examined existing strategies for parallelizing the arithmetic operations on large numbers. We have restructured and refined some of the existing works for better performance for large integers. Additionally, we explored the use of Vedic mathematics, an ancient Indian system of mathematical techniques that offers methods for performing arithmetic operations such as multiplication, division, quotient, and factorization. Vedic mathematical approaches are typically designed for efficient mental calculations; therefore, they are

3

often parallelizable. However, they have not been explored for parallel implementations in large-number arithmetic.

Challenges: The fundamental arithmetic operations, addition and subtraction, are inherently not parallelizable due to carry and borrow dependency; as a result, they are usually implemented sequentially. Thus, it is hard to utilize parallelism for addition and subtraction. However, keeping in mind the applications of large-number arithmetic being predominantly random numbers, such as for cryptography, we have tried to tweak the existing addition and subtraction techniques [Yee19; KS73] for faster parallel execution using SIMD constructs. On the other hand, large-number multiplications are typically implemented using various divide-and-conquer strategies [Kar63; Too63; CA69; SS71] for a smaller number of multiplications to be performed, and as a result, it is harder to compute them in parallel using SIMD constructs. However, existing works tried to leverage SIMD constructs for smaller-sized base-case multiplication utilizing a typical grade-school multiplication technique [Knu97]. In this work, we have utilized the Urdhva Tiryagbhyam sutra [MAH92] for the base-case multiplication instead of the grade-school technique, as it is more loosely coupled in nature.

**Contributions:** In this work, we have made the following key contributions:

- Proposed an improved addition and subtraction technique for large numbers, enabling parallel computations in most cases.

- Proposed a hybrid divide-and-conquer method incorporating the Urdhva Tiryagbhyam technique from Vedic Mathematics as base-case for large-number multiplication.

- Implemented the proposed addition and subtraction using AVX512 intrinsics, achieving an average execution time speed-up of 2.06× and 2.32× over the GNU Multiple Precision (GMP) library for operand sizes ranging from 256 to 1,31,072 bits on an Intel Rocket Lake-based CPU.

- Implemented the proposed base-case Vedic-based multiplication using AVX512 for fixed 256-bit operands and achieved a 1.83x execution time speed-up compared to GMP on the same Intel CPU.

- Additionally, introduced an approximate version of our addition and subtraction approach, which further enhances performance, achieving an average speed-up of 2.52× for addition and 2.80× for subtraction compared to GMP.

Organization of the Thesis: Chapter 2 provides background information and reviews related literature. Chapter 3 introduces the proposed technique for large number addition, including its implementation details and observations. Following this, Chapter 4 discusses the proposed techniques for large number subtraction, along with the implementation and observations. In Chapter 5, we present approximate variants of the proposed addition and subtraction approaches. The hybrid technique that incorporates Vedic mathematics for large integer multiplication is described in Chapter 6, along with the implementation and performance observations of this Vedic approach. Chapter 7 offers an overall discussion of the three operations, addressing the limitations and challenges encountered. Finally, Chapter 8 concludes the work.

### **Chapter 2**

# **Background & Related Works**

#### 2.1 Large Numbers

Typical programming languages like C, C++, Java, and JavaScript have native support for variables ranging from 8-bit to 64-bit (equivalent to storing two hex-digits to 16 hex-digits), depending on the versions and the architecture. However, many real-world applications, particularly cryptography and scientific computing, may require numbers exceeding these 64-bit limits.

In this context, "large numbers" refer to values beyond the standard 64-bit-and-beyond capabilities of common programming languages required for arbitrary precision. As outlined in Problem Statement 1.1, our focus is on performing arithmetic operations on these large, randomly generated numbers as fast as possible, keeping in mind the application needs.

Use Cases: Classical cryptographic applications like Elliptic Curve Cryptography (ECC) [Mil86] typically operate on 256-bits to 521-bits [IBM], RSA [RSA78] currently utilizes operand sizes ranging between 2048 to 3072 bits [Teab; Hou], Diffie-Hellman Key Exchange [DH22] is currently recommended between 2048-bit to 3072-bit [Bar20]. However, the rise of quantum computing necessitates post-quantum cryptography (PQC) [BL17], which relies on significantly larger key sizes to ensure security against quantum attacks. For example, CRYSTALS-Kyber [Bos+18] (Key Encapsulation Mechanism) requires public keys roughly equivalent to 6144 to 12544 bits [Ala+22], CRYSTALS-Dilithium [Lyu+20] (Digital Signature) uses public keys equivalent to approximately 8704 to 20736 bits, and signatures equivalent to 16384 to 36760 bits [Ala+22], Falcon [Fou+18] (Digital Signature), a lattice-based signature, has public keys of roughly 7176 to 14936 bits and signatures of 5328 to 9832 bits [Ala+22], SPHINCS+ [Ber+15] (Digital Signature) exhibits signature sizes ranging from 62848 to 398848 bits, and public keys of 256 or 512 bits [Ala+22].

These necessitate the need to speed up the fundamental arithmetic operations like addition, subtraction, and multiplication for better performance with the usage of current hardware enhancements, as working with such large numbers can be time-consuming; even small performance gains would be for the greater good.

#### 2.1.1 Large Number Representation

Typical cryptographic arithmetic libraries, such as GMP, adopt a limb-based representation for managing large integers. A *limb* is a fixed-size unit, typically a 32-bit or 64-bit unsigned integer, often matching the machine word size that stores a portion of the number. Multiple limbs collectively represent the full integer, stored as a contiguous array for large numbers or as a set of registers for smaller ones. The base used for limb representation determines the number of bits that can be stored

2.2. Addition 5

within each limb. Ideally, while distributing the large numbers across 32- or 64-bit limbs, one would use  $2^{32}$  or  $2^{64}$  as its base for minimizing the number of limbs (i.e. if any library is utilizing hex numbers, 32-bit can hold eight hex-digits, and 64-bit can hold 16 hex-digits, effectively making the base for the whole limb as  $2^{32}$  or  $2^{64}$ ).

However, certain cryptographic implementations, such as those used for elliptic curve cryptography (ECC), benefit from using bases other than 2<sup>32</sup> or 2<sup>64</sup>. This leads to an unsaturated representation, also called reduced-radix, where some bits within each limb remain unused. For instance, implementations of the P-256 elliptic curve often utilize unsaturated limbs. Conversely, saturated representations, or native-radix, utilize all available bits within each limb [RSS23]. The work by Erbsen et al. [Erb+20] highlights these unsaturated implementations and, for their implementation for ECC, they utilize unsaturated limbs. The work also highlights that certain representations, such as Curve25519 [Ber06], utilize mixed-radix bases. Instead of all limbs having a fixed number of bits utilized, also known as uniform-radix base, we may have an alternate pattern of bits utilized. For e.g. base  $2^{25.5}$  for 32-bit Curve25519 contains 26 bits in the first limb, 25 bits in the second, 26 bits in the third, and so on. This kind of unorthodox base sometimes helps for faster performance. As highlighted by Ersben et al. [Erb+20], modular reduction by  $2^{255} - 19$  is fastest when the 255th bit of a large number aligns with the first bit of a limb. In a saturated implementation, limb boundaries align with multiples of the integer size (e.g., a 64bit saturated representation places boundaries at bits 0, 64, 128, etc.). However, in an unsaturated implementation with an unconventional base like 225.5, limb boundaries occur at bits 0, 26, 51, 77, ... and 255. The significant speed boost in modular reduction justifies using a little extra memory to store each large number.

In our work, we have opted for 64-bit limbs to match the machine word size of modern CPUs (x86-64 based). While our addition, subtraction, and multiplication algorithms are designed to be independent of limb size and limb saturation, for addition and subtraction, we have employed saturated and uniform representation, utilizing all the 64-bits with an effective base of  $2^{64}$ . However, for multiplication, we have used a 52-bit unsaturated and uniform representation, with an effective base of  $2^{52}$ , to accelerate our multiplication implementation, which we have discussed in the implementation section of Chapter 6.

#### 2.2 Addition

#### 2.2.1 Carry Propagate Addition

A method for performing addition is through digit-by-digit carry propagation. In large-number additions, the two numbers to be added may typically contain up to 16,384 hex digits if we're handling 65,536-bit numbers. If we process each digit at once, as depicted in eq. 2.1 [Knu97], that will result in 16,384 additions between two operands and 16,383 carry propagations (ignoring the initial carry).

$$S_i = A_i + B_i + C_{i-1}, (2.1)$$

$$C_i = \begin{cases} 1, & \text{if } S_i \ge B_{\text{max}}, \\ 0, & \text{otherwise.} \end{cases}$$

(2.2)

In the above equations,  $S_i$  denotes the intermediate sum at position i, computed by adding the corresponding digits  $A_i$  and  $B_i$  along with the carry from the previous position,  $C_{i-1}$ . The carry for the next position,  $C_i$ , is set to 1 if the intermediate sum

exceeds or equals the base limit  $B_{\text{max}}$ ; otherwise, it remains 0. Here,  $B_{\text{max}}$  represents the numerical base limit (e.g., 16 for hex digits).

But, most library implementations [GNU91; Docd; PYP; Docb] pack multiple digits together in a single limb instead of just a bit or digit, be it saturated or unsaturated, i.e., instead of treating each hex digit separately, we can combine multiple hex digits into a larger group, thereby reducing the number of required operations.

#### Example 2.2.1.1.

Consider the addition of two eight-digit hexadecimal numbers:

$$A = 7F93BC2D$$

,  $B = 4E87A9F6$ .

We perform the digit-wise addition from right to left:

Since we are working in base 16, any sum  $S_i \ge 0xF$  generates a carry. Extracting the individual carries:

Here, each carry only affects its preceding digit. However, if we group the digits into two groups of four digits each, we reduce the carry propagations, as we only need to propagate just two carry instead of seven:

The carry from the right group (16613) only affects the left group if the sum exceeds four hex digits (i.e.,  $S_i > 0xFFFF$ ). This method localizes carry propagation within smaller groups, reducing the total number of carry propagations. The more digits are grouped together, the fewer additions and carry propagations.

Modern computer Instruction Set Architectures (ISA) are typically designed to process data in 32-bit or 64-bit format. For instance, a 32-bit *limb* can represent values up to 0*xFFFFFFFF*. This allows us to combine eight consecutive hex digits into one 32-bit limb, and carry propagation within the limb is handled by the hardware adders themselves; we only need to account for carry if the sum overflows. This approach will reduce the number of arithmetic operations required as more digits are processed in each operation, thereby improving computational performance. For example, by grouping the digits into 32-bit limbs, the 16,384 hex-digit number is represented using only 2,048 limbs. So, now, we can perform the addition of the two 16384 hex-digit numbers with just 2048 additions and 2047 carry propagations.

Almost all libraries, including GMP, utilize the carry-propagation addition algorithm mentioned in eq. 2.1, sequentially propagating the carry for each subsequent limb addition. However, this sequential carry propagation is a major issue in terms of parallelizing the additions.

#### 2.2.2 Carry Select Addition

In the carry propagation method, the current addition must wait for the previous addition to finish generating its carry, causing a delay. To address this issue, carry

2.3. Subtraction 7

select addition [Bed62] was introduced, primarily in the circuits. Carry-select addition addresses this by pre-computing two possible results for each digit, covering both scenarios for the incoming carry  $C_{i-1}$ , which can be either 0 or 1:

• If there's no carry-in ( $C_{i-1} = 0$ ):

- Sum:

$$S_i^{(0)} = (A_i + B_i) \mod B_{max}$$

,

- Carry-out:

$$C_{i+1}^{(0)} = (A_i + B_i)/B_{max}$$

,

• If there's a carry-in  $(C_{i-1} = 1)$ :

- Sum:

$$S_i^{(1)} = (A_i + B_i + 1) \mod B_{max}$$

- Carry-out:

$$C_{i+1}^{(1)} = (A_i + B_i + 1)/B_{max}$$

.

Once the actual  $C_{i-1}$  from the previous digit is known, the correct sum and carry-out are selected:

$$S_i = S_i^{(C_{i-1})}, \quad C_{i+1} = C_{i+1}^{(C_{i-1})}.$$

(2.3)

By pre-computing both outcomes in advance, this approach avoids waiting for the carry to propagate, primarily in the hardware circuits. However, it incurs double the cost due to computing two possibilities for software implementation and computing them in parallel using multi-threading may incur overhead costs. Nonetheless, a long-chained dependency may still persist for software implementation to select the correct sums and carry-outs from the least to the most significant digit, limiting full parallelization.

#### 2.3 Subtraction

Subtraction is similar to addition; instead of propagating carries, we generate borrows. We can tweak the carry propagation equation (Eq. 2.1) for subtraction as depicted in Eq. 2.4.

$$D_i = X_i - Y_i - B_{i-1}, (2.4)$$

$$B_i = \begin{cases} 1, & \text{if } X_i - Y_i - B_{i-1} < 0, \\ 0, & \text{otherwise.} \end{cases}$$

(2.5)

This still causes the same long-chained dependency as for carry-propagation addition. Similarly, the borrow-select subtraction tackles the waiting dependency of the previous borrow to be generated by pre-computing two possible results for each digit, covering both scenarios for the incoming borrow  $B_{i-1}$ , which can be either 0 or 1:

• If there's no borrow-in  $(B_{i-1} = 0)$ :

- Difference:

$$D_i^{(0)} = (X_i - Y_i) \mod B_{max}$$

,

- Borrow-out:

$$B_i^{(0)} = \begin{cases} 1, & \text{if } X_i - Y_i < 0, \\ 0, & \text{otherwise,} \end{cases}$$

• If there's a borrow-in  $(B_{i-1} = 1)$ :

- Difference:

$$D_i^{(1)} = (X_i - Y_i - 1) \mod B_{max}$$

,

- Borrow-out:

$$B_i^{(1)} = \begin{cases} 1, & \text{if } X_i - Y_i - 1 < 0, \\ 0, & \text{otherwise,} \end{cases}$$

#### 2.4 Multiplication

Performing multiplication on large numbers is computationally heavier than addition or subtraction, as it incurs many more computations. Popularly, there are two approaches for computing multiplication: the simple school-book technique and divide-and-conquer-based strategies. Other approaches are not very practical for our targeted operand sizes. The following subsections discuss them in detail.

#### 2.4.1 Grade-school

Grade school multiplication [Knu97], sometimes called schoolbook or grammar school multiplication, is the basic and conventional method of multiplying numbers by arranging a rectangle of cross-products. It's exactly like the long multiplication we do with pencil and paper.

The grade-school multiplication technique for  $X \times Y$  is described as follows. Let X have n digits  $(X_0, X_1, \ldots, X_{n-1})$  and Y have m digits  $(Y_0, Y_1, \ldots, Y_{m-1})$ , in base B (e.g., B = 10 for decimal). For each position  $k = 0, 1, \ldots, n + m - 1$ :

1. Compute the sum at position *k*:

$$S_k = \sum_{\substack{i,j\\i+j=k}} X_i \cdot Y_j + C_{k-1},$$

where  $C_{-1} = 0$  initially.

2. Compute the carry to the next position:

$$C_k = |S_k/B|$$

,

3. Compute the digit at position *k*:

$$P_k = S_k \mod B$$

.

The final product is  $P = P_0 P_1 \cdots P_{n+m-1}$ , where:

- $S_k$ : Sum at position k,

- $C_k$ : Carry to position k + 1,

- $P_k$ : Digit at position k.

Although this method has a time complexity of  $O(n \cdot m)$ , where n and m represent the sizes of the operands, it is still the preferred choice in many libraries and implementations (e.g., [GNU91; Docc; Docb; ET20; ET23]) for smaller large numbers. Faster divide-and-conquer strategies, despite having better time complexity, suffer from performance degradation when dealing with moderately sized numbers. As a result, this technique proves to be more practical in those cases. Notably, GMP version 6.3.0 typically uses the grade-school multiplication method for smaller numbers and adopts divide-and-conquer strategies for larger numbers.

9

#### 2.4.2 Divide-and-Conquer Multiplication Strategies

#### Karatsuba

The Karatsuba multiplication algorithm, as described in Knuth's book [Knu97], employs a divide-and-conquer strategy for multiplying two large numbers, X and Y. The algorithm recursively splits each number into two halves of equal length: X is divided into  $X_H$  (the high-order half) and  $X_L$  (the low-order half), while Y is divided into  $Y_H$  (the high-order half) and  $Y_L$  (the low-order half). In contrast to the traditional grade-school method, which requires four multiplications at each recursive step (specifically,  $X_H \times Y_H$ ,  $X_H \times Y_L$ ,  $X_L \times Y_H$ , and  $X_L \times Y_L$ ), the Karatsuba algorithm reduces the total to just three multiplications:  $X_H \times Y_H$ ,  $X_L \times Y_L$ , and  $(X_H + X_L) \times (Y_H + Y_L)$ . This optimization effectively saves one multiplication for each recursive step. The algorithm then combines these results with less costly computations, as outlined next.

The Karatsuba approach can be expressed as follows for two n-digit numbers X and Y, where n is assumed to be a power of 2 for simplicity:

- Split  $X = X_H \cdot B^{n/2} + X_L$  and  $Y = Y_H \cdot B^{n/2} + Y_L$ , where B is the base (e.g., B = 16 for hexadecimal), and n/2 is the split point.

- Compute three recursive products:

- 1.  $P_1 = X_H \times Y_H$

- 2.  $P_2 = X_L \times Y_L$

- 3.  $P_3 = (X_H + X_L) \times (Y_H + Y_L)$ .

- Combine results:  $X \times Y = P_1 \cdot B^n + (P_3 P_1 P_2) \cdot B^{n/2} + P_2$ .

The base case occurs when n=1, where X and Y are single digits, and the multiplication is direct (i.e.,  $X \times Y$ ).

To save up some operations like carry-overflows while performing the addition for  $(X_H + X_L) \times (Y_H + Y_L)$ , GMP utilizes subtraction instead of addition, like  $(X_H - X_L) \times (Y_H - Y_L)$ . Their strategy [Kar] is depicted below:

For two *N*-limb numbers *X* and *Y* (where *N* is even for simplicity):

- Define k = N/2, and set  $b = 2^{k \cdot \text{bits\_per\_limb}}$ , where bits\\_per\_limb is 64 on x86\_64 CPUs.

- Split  $X = X_1 \cdot b + X_0$  and  $Y = Y_1 \cdot b + Y_0$ , where  $X_0, X_1, Y_0, Y_1$  are k-limb numbers.

- Compute three recursive products:

- 1.  $P_1 = X_1 \times Y_1$ ,

- 2.  $P_2 = X_0 \times Y_0$ ,

- 3.  $P_3 = (X_1 X_0) \times (Y_1 Y_0)$  (noting that if  $X_1 < X_0$  or  $Y_1 < Y_0$ , the result may be negative).

- Combine results:

$$X \cdot Y = (b^2 + b) \cdot P_1 - b \cdot P_3 + (b+1) \cdot P_2 \tag{2.6}$$

• Base case: If  $N = \theta$ , perform grade-school multiplication.

Karatsuba's time-complexity is  $O(n^{1.585})$ ), as on each halved-recursion, it performs three multiplications ( $O(n^{log_23})$ ). For most modern CPUs, GMP utilizes Karatsuba for equal-length operands with a number of limbs between 20 and 130.

#### Toom-Cook

Toom-Cook multiplication [Too63; CA69; Knu97] is more of a generalized approach of Karatsuba [Kar63]. Instead of splitting the number into two equal lengths, Toom multiplications splits them into n halves; typically, three and four halves are the most popular ones.

**Toom-3 Way** For two *N*-limb numbers *X* and *Y*, Toom-3 [Too] splits them into three parts as follows:

• Represent *X* and *Y* as:

$$X = [x_2 \mid x_1 \mid x_0],$$

$Y = [y_2 \mid y_1 \mid y_0],$

where  $x_0$ ,  $x_1$ ,  $y_0$ ,  $y_1$  are k-limb pieces (roughly N/3 limbs each), and  $x_2$ ,  $y_2$  may be 1 or 2 limbs shorter.

• Express X = X(b) and Y = Y(b) as polynomials:

$$X(t) = x_2t^2 + x_1t + x_0$$

,  $Y(t) = y_2t^2 + y_1t + y_0$

The product  $X \cdot Y = W(b)$ , where  $W(t) = X(t) \cdot Y(t) = w_4 t^4 + w_3 t^3 + w_2 t^2 + w_1 t + w_0$ . The coefficients  $w_i$  (each roughly  $b^2$  in size) are determined by evaluating W(t) at five points and then solving a system of equations. The final result is:

$$W(b) = w_4 b^4 + w_3 b^3 + w_2 b^2 + w_1 b + w_0$$

The algorithm proceeds as follows:

- 1. **Split Operands**: Divide *X* and *Y* into  $[x_2, x_1, x_0]$  and  $[y_2, y_1, y_0]$ , with  $k \approx N/3$  limbs per part (adjusting for  $x_2, y_2$ ).

- 2. **Evaluate at Five Points**: Compute  $W(t) = X(t) \cdot Y(t)$  at:

- t = 0:  $W(0) = x_0 \cdot y_0 = w_0$ ,

- t = 1:  $W(1) = (x_2 + x_1 + x_0) \cdot (y_2 + y_1 + y_0)$ ,

- t = -1:  $W(-1) = (x_2 x_1 + x_0) \cdot (y_2 y_1 + y_0)$  (use absolute values and track sign if negative),

- t = 2:  $W(2) = (4x_2 + 2x_1 + x_0) \cdot (4y_2 + 2y_1 + y_0)$ ,

- $t = \infty$ :  $W(\infty) = x_2 \cdot y_2 = w_4$  (limit as  $t \to \infty$ , effectively  $X(t) \cdot Y(t) / t^4$ ).

- 3. **Form Linear System**: Substitute the points into W(t):

$$W(0) = w_0,$$

$$W(1) = w_4 + w_3 + w_2 + w_1 + w_0,$$

$$W(-1) = w_4 - w_3 + w_2 - w_1 + w_0,$$

$$W(2) = 16w_4 + 8w_3 + 4w_2 + 2w_1 + w_0,$$

$$W(\infty) = w_4.$$

- 4. **Solve for Coefficients**: Solve the system:

- $w_0 = W(0)$ ,

- $w_4 = W(\infty)$ ,

- $w_1 = \frac{W(1) W(-1) 2w_4}{2}$

- $w_3 = \frac{W(1) + W(-1) 2w_0 2w_4}{2}$

- $w_2 = \frac{W(2) 16w_4 8w_3 2w_1 w_0}{4}$

2.5. Vedic Mathematics

5. **Combine**: Compute  $X \cdot Y = w_4b^4 + w_3b^3 + w_2b^2 + w_1b + w_0$ .

This requires five multiplications of roughly N/3-limb numbers, compared to nine in a base-case approach, offering time-complexity  $O(n^{log_35}) \sim O(N^{1.465})$ .

11

**Toom-4 Way** As the name suggests, Toom-4 splits up the operands into four similar-length parts:

$$X = [x_3 \mid x_2 \mid x_1 \mid x_0],$$

$Y = [y_3 \mid y_2 \mid y_1 \mid y_0],$

And, in a similar fashion to Toom-3, it computes the product, but with a time-complexity of  $O(n^{\log_4 7})$ , as it performs seven multiplications in total for the four splits, effectively performing in  $O(n^{1.404})$ .

The higher degree Toom-n takes more pieces, resulting in fewer multiplications compared to the grade-school technique, dropping the time complexity from  $O(n^2)$  to something like  $O(n^{\log_n(2n-1)})$ . GMP 6.3.0 uses versions like Toom-3 (3 pieces), Toom-4 (4 pieces), and even Toom-6'n'half or Toom-8'n'half for larger numbers. For reference, Toom-2 (which is equivalent to the Karatsuba method) starts at 19 limbs, Toom-3 at 125 limbs, Toom-4 at 196 limbs, Toom-6'n'half at 276 limbs, and Toom-8'n'half at 369 limbs for AMD Zen 2 architecture.

#### 2.4.3 Fast Fourier Transformation

The idea of using the Fast Fourier Transform (FFT) for multiplication got its start with Schönhage and Strassen in 1971 [SS71], who used FFT to multiply huge integers in  $O(n \log n)$  time, even faster than Toom-n. Details of FFT multiplication are not mentioned in this work. But for instance, for FFT multiplication, GMP handles the product as  $x \cdot y \mod 2^N + 1$ , splitting numbers into  $2^k$  pieces of  $N/2^k$ -bit chunks. This requires  $2^k$  pointwise multiplications, dropping the time complexity to  $O(n^{k/(k-1)})$  for a modular result. Padding with zeros gives the full product, and GMP picks k based on size: k = 4 kicks in around 300–1000 limbs, while k = 8 takes over at 3000–10000 limbs for full products on modern CPUs.

#### 2.5 Vedic Mathematics

Vedic Maths is an ancient Indian system of mathematical principles and techniques that evolved in India about 5,000 years ago. It was rediscovered by Indian mathematician Jagadguru Shri Bharati Krishna Tirthaji and later documented in his writings [MAH92]. The system is rooted in the ancient scriptures of India, known as the Vedas, and comprises 16 sutras (formulas) and 13 sub-sutras (corollaries). The formulae and their application are known for solving complex arithmetical operations mentally. The thirteen sub-sutras and corollaries are based on the primary sixteen sutras; specifics are not listed here. For our work, we have found the Urdhva-Tiryagbhyam sutra, the third sutra, ideal for multiplication, which we will discuss next. A summary of the sixteen sutras is mentioned in table 2.1.

| No. | Sutra                           | Usage                                                                      |

|-----|---------------------------------|----------------------------------------------------------------------------|

| 1   | Ekadhikena Purvena              | "by one more than the previous one" for efficient                          |

|     |                                 | multiplication or division by 2, and many more                             |

|     |                                 | arithmetic operations.                                                     |

| 2   | Nikhilam Navatascaramam Dasatah | "all from 9 and the last from 10" for multiplication                       |

|     |                                 | and division, especially near powers of 10.                                |

| 3   | Urdhva-Tiryagbhyam              | "vertically and crosswise" techniques for multipli-                        |

|     |                                 | cation, argumental division, and straight division.                        |

| 4   | Paravartya Yojayet              | "transpose and apply" for division, simple equa-                           |

|     |                                 | tions, mergers, multiple simultaneous equations, si-                       |

|     |                                 | multaneous quadratic equations, and partial frac-                          |

|     |                                 | tions.                                                                     |

| 5   | Sunyam Samyasamuccaye           | "when the samuccaya is the same, it is zero" for                           |

|     |                                 | solving simple and quadratic equations.                                    |

| 6   | (Anurupye) Sunyamanyat          | "if one is in ratio, the other is zero" for solving si-                    |

|     |                                 | multaneous simple equations, quadratic equations,                          |

|     |                                 | and simultaneous quadratic equations.                                      |

| 7   | Sankalana-vyavakalanabhyam      | "by addition and by subtraction" to solve simulta-                         |

| - 0 | D                               | neous linear equations.                                                    |

| 8   | Puranapuranabhyam               | "by the completion or non-completion" for cubic and biquadratic equations. |

| 9   | Calana-kalanabhyam              | "sequential motion" (specific applications not fully                       |

| 9   | Calana-kalanabnyam              | listed).                                                                   |

| 10  | Yavadunam                       | "whatever the deficiency" for squaring, cubing,                            |

| 10  | Tavadunam                       | square roots, and cube roots.                                              |

| 11  | Vyastisamastih                  | "specific and general" for solving biquadratic and                         |

| 11  | vyastisaittastiit               | multiple simultaneous equations.                                           |

| 12  | Sesanyankena Caramena           | "remainder by the last digit" for quotient-digit com-                      |

| 12  | Sesariyarixeria Carafferia      | putations.                                                                 |

| 13  | Sopantyadvayamantyam            | "the ultimate and twice the penultimate" for miscel-                       |

| 10  |                                 | laneous simple equations.                                                  |

| 14  | Ekanyunena Purvena              | "by one less than the previous one" (specific appli-                       |

|     | ,                               | cations not fully listed).                                                 |

| 15  | Gunitasamuccayah                | "the product of the sum" (specific applications not                        |

|     | ĺ                               | fully listed).                                                             |

| 16  | Gunakasamuccayah                | To solve differential calculus through "the factor of                      |

|     |                                 | the sum."                                                                  |

|     |                                 |                                                                            |

${\it TABLE~2.1: Summary~of~the~Sixteen~Vedic~Sutras}$

13

#### 2.5.1 Urdhva-Tiryagbhyam Sutra for Multiplication

Urdhva-Tiryagbhyam Sutra, also known as Urdhva-Tiryak Sutra, as mentioned in chapter 3 of the book [MAH92], is a generalized multiplication formula that applies to all cases of multiplication and is also useful for the division of two large numbers. The sutra basically simplifies to "vertically and cross-wise". It divides the large integer multiplication into multiple sets of short and simple multiplications.

#### Example 2.5.1.1.

An instance is shown below for multiplying using the Urdhva-Tiryagbhyam technique:

Step 1: First, we take the most significant digit of both operands, then take two digits from the most significant position, and then take the least significant digit of both operands. Basically, creating prefix and suffix sets from left to right.

Step 2: Next, we cross-multiply the individual digits within each set that we formed in Step 1 and add the partial products within each such set.

$$(2 \times 3)$$

,  $(2 \times 6) + (9 \times 3)$ ,  $(9 \times 6)$

Step 3: After Step 2, if the partial sums are greater than 9, we carry over the extra digits from right to left partial sums (i.e. from least significant set to most significant set). This step is also known as *suddhikaran*. In this case,

Next, we will propagate 5 from the right-most-hand-set and add it to the middle set, then from the middle set and so on.

Now, as the left-most-hand number is greater than 9 (as we are working with base 10), we'll create one extra digit.

Hence, the answer for the multiplication is 1044. We take another example of three digits:

Applying Step 1, forming the prefix and suffix sets.

Next, we cross-multiply the individual digits within each set as in Step 3.

FIGURE 2.1: Urdhva-Tiryagbhyam Multiplications (set-wise) [Upa]

We then carry over extra digits from right to left:

(2), (0), (4), (2), (8), (2)

Thus, the result is 204282.

Figure 2.1 simplifies the multiplications to be performed; each color represents the multiplications within a set. Most practitioners of Vedic Mathematics often find the steps straightforward enough, with some practice, to perform all calculations for large multiplications mentally in just a few seconds. We have formalized the algorithm for Urdhva-Tiryagbhyam multiplication and have provided a detailed description here, Algorithm 1.

#### Example 2.5.1.2.

To compare the grade-school and Urdhva-Tiryagbhyam multiplication methods, let's look at multiplying 843 by 384.

#### Grade-School Multiplication: $843 \times 384$

Note: in the context of large numbers, multiplications like  $843 \times 4$  can't be performed directly, as the size of the multiplicand 843 can be more than the native limb size of a machine. Hence, we need to break the multiplicand into small parts and add the partial products to form the resultant product. The operation count below assumes breaking up the multiplicand into individual digits; in order to form the partial multiplication result, we need to propagate the carries.

#### **Operation counts:**

- Multiplications:  $3 \times 3 = 9$  (each digit of 843 multiplied by each digit of 372)

- Carry additions during multiplication: 2 + 2 + 2 = 6

- Column-wise additions: 1+2+2+1=6

- Column-wise carry additions: 1+1+1+1=4

#### Generalized Form:

• Multiplications:  $n \times n = n^2$

15

- Carry additions inside digit multiplications:  $n \times (n-1)$

- Column-wise additions:  $\sum_{i=0}^{n-1} i + \sum_{i=0}^{n-1} i = n \times (n-1)$

- Column-wise carry additions: 2n 1

#### Urdhva-Tiryagbhyam Multiplication: 843 × 384

#### **Digit Sets:**

- For 843: 8, 84, 843, 43, 3

- For 384: 3, 38, 384, 84, 4

#### **Cross-Products:**

$$8 \times 3 = 24$$

,

$(8 \times 8) + (4 \times 3) = 64 + 12 = 76$ ,

$(8 \times 4) + (4 \times 8) + (3 \times 3) = 32 + 32 + 9 = 73$ ,

$(4 \times 4) + (3 \times 8) = 16 + 24 = 40$ ,

$3 \times 4 = 12$ .

#### **Partial Products:**

#### After suddhikaran (Carry Propagation):

2, carry 1,

$$40 + 1 = 41 \Rightarrow 1$$

, carry 4,

$73 + 4 = 77 \Rightarrow 7$ , carry 7,

$76 + 7 = 83 \Rightarrow 3$ , carry 8,

$24 + 8 = 32 \Rightarrow 2$ , carry 3,

3 (new digit)

#### **Final Result:**

$$[3,1,3,7,1,2] = 323712$$

For additions within the sets, we have assumed the adder can perform two two-digit operand additions at a time, and some additions may produce results of three digits, which can be accounted for later by checking the wrap-around of the result (e.g. 81+64+49 would produce results of three digits).

#### **Operation Counts:**

- Multiplications: 1 + 2 + 3 + 2 + 1 = 9

- Additions within sets: 0 + 1 + 2 + 1 + 0 = 4

- Carry-Additions during suddhikaran: 4

#### **Generalized Form:**

- Multiplications:  $n \times n = n^2$

- Additions within sets:  $\sum_{i=0}^{n-1} i + \sum_{i=0}^{n-2} i = (n-1)^2$

- Carry-Additions during suddhikaran: 2n 1

#### Algorithm 1: Urdhva-Tiryagbhyam Multiplication

```

Input: Two n-digit numbers X and Y in base 10.

Output: Product P = X \times Y.

// Step 1: Form prefix sets for both numbers

for len \leftarrow 1 to n do

Form prefix set P_{X,len} from X with length len;

Form prefix set P_{Y,len} from Y with length len;

// E.g., for 873: prefix sets

are 8, 87, 873

// Step 2: Form suffix sets for both numbers

for len \leftarrow n-1 to 1 do

Form suffix set S_{X,len} from X with length len;

Form suffix set S_{Y,len} from Y with length len;

// E.g., for 873: suffix sets

are 73, 3

// Step 3: Merge prefix and suffix sets into merged sets

M_X \leftarrow [P_{X,1}, \dots, P_{X,n}, S_{X,n-1}, \dots, S_{X,1}], M_Y \leftarrow [P_{Y,1}, \dots, P_{Y,n}, S_{Y,n-1}, \dots, S_{Y,1}];

// E.g., for 873: M_{X} = [8, 87, 873, 73, 3]

// Step 4: Compute cross-products for each pair of merged sets

for i \leftarrow 1 to 2n - 1 do

R_i \leftarrow 0;

index_X \leftarrow 0;

index_Y \leftarrow length of M_{Y,i} - 1;

// Multiply and add from both ends moving inward

while index_X < length \ of \ M_{X,i} and index_Y \geq 0 do

R_i \leftarrow R_i + (M_{X,i}[index_X] \times M_{Y,i}[index_Y]);

index_X \leftarrow index_X + 1;

index_Y \leftarrow index_Y - 1;

// Step 5: Perform suddhikaran (carry-over extra digits)

carry \leftarrow 0;

for i \leftarrow (2n-1) to 1 (right to left) do

R_i \leftarrow R_i + carry;

if R_i \geq 10 then

carry \leftarrow \lfloor R_i/10 \rfloor;

R_i \leftarrow R_i \mod 10;

else

carry \leftarrow 0;

if carry > 0 then

Prepend carry as an extra digit to the result;

// Step 6: Combine digits to form the final product

Combine digits in R to form the product P;

return P;

```

**Operation Count Summary for** n**-Digit Numbers:** The table 2.2 summarizes the number of operations required for multiplying two n-digit numbers. Effectively, the time complexity for Urdhva-Tiryagbhyam is  $O(n^2)$  as it performs  $n^2$  multiplications. But, if we disregard the additional carries during partial product addition of the grade-school, the Urdhva-Tiryagbhyam method minimizes operations, requiring (n-1) fewer additions than grade-school multiplication. Both algorithms are slower in terms of time complexity as compared to the divide-and-conquer methods that we have seen, but for not-so-large numbers, implementation-wise, they are typically faster due to the overhead cost of recursion.

As the Urdhva-Tiryagbhyam method natively breaks large numbers into smaller sets of individual digit multiplications (loosely coupled), it's much more effective

| Operation       | Grade-School     | Urdhva-Tiryagbhyam |

|-----------------|------------------|--------------------|

| MUL             | $n^2$            | $n^2$              |

| ADD             | n(n-1)           | $(n-1)^2$          |

| Carry-ADD       | 2n - 1           | 2n - 1             |

| Extra-Carry-ADD | $n \times (n-1)$ | 0                  |

TABLE 2.2: Operation counts for grade-school and Urdhva-Tiryagbhyam multiplication of two *n*-digit numbers.

for large numbers and was popular among practitioners from ancient times for the mental multiplication of large numbers.

Usage of Viniculum Since Vedic Mathematics is intended for faster mental mathematics, we typically use the Viniculum technique for multiplying digits greater than 5. The Viniculum is similar to finding the 9's complement of a number. After applying the Vinculum to the operands, we multiply the digits as usual, but with the advantage that all digits are reduced to less than 6, making them easier to compute mentally. Afterwards, we convert the intermediate result back to its original form by applying the vinculum again, effectively normalizing it. Although this method can be faster for mental computation, depending on the numbers involved, it may not offer advantages when implemented in a computer program, as hardware circuits remain unaffected, as all the values stay within a given base. Consequently, it might not be relevant to our work.

#### 2.6 Related Works on Parallel Arithmetic for Large Numbers

#### 2.6.1 Addition and Subtraction

The task of parallelizing the addition operation remains challenging due to the direct dependency of carry in subsequent digit additions when adding two numbers. As a typical carry-propagation addition algorithm computes carry  $C_i$  for  $i^{th}$  place after the successful calculation of  $S_{i-1}$ , which again depends upon  $C_{i-1}$  (as depicted in Eq. 2.1), thereby creating a carry propagation dependency. This dependency may create performance bottlenecks, as each digit addition must wait for the previous carry to be generated before proceeding, which is not at all ideal for parallelizing the add operations. The alternative approach of carry-select additions is not widely used due to the heavy overhead in computing both possibilities. Consequently, many fast arithmetic libraries ([GNU91]) do not leverage parallel computation in their addition implementations for large numbers. However, we may skip the involvement of carries while adding two operands and later account for the carry. But, in certain scenarios, we may have to sequentially add the carries from the least significant digit to the most significant digit, as each digit carry adjustment may generate further carries, creating a chained sequential dependency. For an N-digit number, even if we group them with K-digits, we still need to sequentially propagate nearly  $\lceil N/K \rceil$ carries.

Some progress has been made to parallelize the operations compared to Eq. 2.1. As shown by Alexander Yee's work for y-cruncher [Yee19], we can utilize the Kogge-Stone adder technique [KS73], which is based on the carry propagation method, to handle carries at a later stage. The idea is to perform the initial addition without considering carries, then detect both the carries and instances where the intermediate sum reaches the maximum value (max-sum) for the base (denoted  $B_{max}$ ). Based

on this detection, we adjust the intermediate sums to account for carries where necessary (intermediate sum adjustment), thus avoiding the need for repeated carry propagation while doing the addition. However, some sequential operations still need to be performed on the carries and the max-sum detection values. As illustrated in Algorithm 2, after computing the intermediate sums  $S_i = X_i + Y_i$  and detecting carry  $(C_i)$  and max-sum  $(M_i)$  conditions in parallel, we must sequentially process these masks from the least significant blocks to the most significant blocks. This sequential step in Phase 3, operating over m blocks, determines which  $S_i$  values require a +1 adjustment, introducing a dependency on the propagating carry that in some way stalls the desired full parallelism. Notably, the implementation mentioned by Yee [Yee19] for the algorithm 2 attempts to eliminate the sequential carry adjustment in Phase 3 of Algorithm 2. However, it does so at the expense of additional operations on the mask registers, such as XOR and masked subtraction, which may be inefficient to perform on a very wide microarchitecture, which will, in turn, increase the overall computation time. For such overhead, they claim not to see any performance improvement compared to traditional implementation with add-carry

Algorithm 2: Kogge-Stone Parallel Addition [Yee19; KS73]

```

Input: Two n-digit numbers X and Y in base B, split into m blocks of K digits each,

where X_i, Y_i are the i-th blocks and X_0, Y_0 are the least significant blocks.

Output: Sum S = [S_{m-1}, ..., S_0].

// Phase 1: Addition (Parallel)

for i \leftarrow 0 to m-1 in parallel do

// Add blocks, ignore overflow

S_i \leftarrow X_i + Y_i;

// Phase 2: Detection (Parallel)

for i \leftarrow 0 to m-1 in parallel do

if S_i \geq B^K then

C_i \leftarrow 1;

// Carry

S_i \leftarrow S_i - B^K

else if S_i = B^K - 1 then

M_i \leftarrow 1;

// Max-Sum

C_{i+1}' = C_i, \forall 0 \le i < m-1, C_0' = 0; // Phase 3: Adjustment (Sequential)

// Left-shift Carries by 1 block

carry \leftarrow 0;

for i \leftarrow 0 to m-1 do

if C'_i = 1 or (carry = 1 \land M_i = 1) then

S_i \leftarrow S_i + 1;

// Fix incorrect blocks

if S_i = B^K then

S_i \leftarrow 0;

carry \leftarrow 1;

// Propagate carry

carry \leftarrow 0;

return S;

```

In contrast, the work [RSS23] presents a new addition method in Algorithm 'ProposedAdd', depicted in algorithm 3, utilizing ideas from carry-select addition [Bed62]. To tackle the long carry dependency chain, it breaks down the addition of large integers A and B into a smaller, parallel addition of 8-bit values  $t_i$  and  $p_i$ . Each digit's addition falls into one of three cases: no-carry (N, where  $c_{i+1} = 0$ ), propagate (P, where  $c_{i+1} = c_i$ ), or generate (G, where  $c_{i+1} = 1$ ), based only on the operands. The  $t_i$  and  $p_i$  values are set up to match the carry behaviour of  $A_i + B_i$ , letting carries

be figured out fast across all digits. It starts with intermediate sums  $S_i = A_i + B_i$ , then uses the t + p addition to pull out carries, which adjust  $S_i$  to get the final sum. This skips repeated carry propagation and cuts down on data shuffling by keeping carries handy. Still, figuring out  $t_i$  and  $p_i$  and doing a cross-digit step adds extra work, making it more computationally heavy. They observed a 30% increase in speed with the latest CTIDH implementation, an 11% increase from the most recent CSIDH implementation on AVX-512 processors, and a 7% boost from Microsoft's standard PQCrypto-SIDH for SIKEp503 running on the A64FX architecture.

Everything we've talked about regarding the parallelization of large-number addition can also be applied to subtraction. Instead of propagating carry, we will generate borrows and adjust -1 instead of +1. Similarly, just as we checked for partial results hitting their maximum base value in addition, we will identify whether the partial results reach zero for subtraction. The addition algorithm seen in algorithm 2 can be adapted to the subtraction algorithm as depicted in algorithm 4. Similarly, the addition algorithm by [RSS23] can also be transformed into subtraction.

```

Algorithm 3: Proposed Add: Proposed SIMD addition [RSS23]

```

```

Input: Two n-digit numbers A and B in base B, where A = [A_{n-1}, ..., A_0],

B = [B_{n-1}, \dots, B_0], and A_i, B_i < B^K, with A_0, B_0 as the least significant

Output: Sum S = \sum_{i=0}^{n-1} 2^{i \cdot K} S_i.

// Step 1: Compute intermediate sums (Parallel)

for i \leftarrow 0 to n-1 in parallel do

S_i \leftarrow A_i + B_i;

// Add digits, ignore carry for now

// Step 2: Set up t_i and p_i based on carry cases (Parallel)

for i \leftarrow 0 to n-1 in parallel do

if A_i + B_i < B^K then

t_i \leftarrow \text{value for case } N;

// No-carry case

p_i \leftarrow \text{constant for } N

else if A_i + B_i = B^K - 1 then

t_i \leftarrow \text{value for case } P;

// Propagate case

p_i \leftarrow \text{constant for } P

else if A_i + B_i \geq B^K then

t_i \leftarrow \text{value for case } G;

// Generate case

p_i \leftarrow \text{constant for } G

// Step 3: Compute smaller addition to extract carries

s \leftarrow t + p;

// Add t_i and p_i across all digits

// Step 4: Pull out carries (Includes cross-digit operation)

for i \leftarrow 0 to n-1 do

c_i \leftarrow \text{extract carry from } s_i, t_i, p_i;

// e.g., s_i - t_i - p_i

// Step 5: Adjust intermediate sums with carries (Parallel)

for i \leftarrow 0 to n-1 in parallel do

S_i \leftarrow (S_i + c_i) \mod B^K;

// Final sum per digit

return S = \sum_{i=0}^{n-1} 2^{i \cdot K} S_i;

```

Again, Phase 3 of algorithm 4 poses the same issue as earlier, i.e. sequential operating order from the least significant block to the most significant block.

Algorithm 4: Kogge-Stone Parallel Subtraction [Yee19; KS73]

```

Input: Two n-digit numbers X and Y in base B, split into m blocks of K digits each,

where X_i, Y_i are the i-th blocks and X_0, Y_0 are the least significant blocks.

Also, X \geq Y.

Output: Sub S = [S_{m-1}, ..., S_0].

// Phase 1: Subtraction (Parallel)

for i \leftarrow 0 to m-1 in parallel do

S_i \leftarrow X_i - Y_i;

// Subtract blocks, ignore borrow

// Phase 2: Detection (Parallel)

for i \leftarrow 0 to m-1 in parallel do

if S_i < 0 then

B_i \leftarrow 1;

// Borrow

S_i \leftarrow S_i + B^K

else if S_i = 0 then

M_i \leftarrow 1;

// Min-Sub

B'_{i+1} = B_i, \quad \forall \, 0 \le i < m-1, B'_0 = 0;

// Left-shift Borrows by 1 block

// Phase 3: Adjustment (Sequential)

borrow \leftarrow 0;

for i \leftarrow 0 to m-1 do

if B'_i = 1 or (borrow = 1 \land M_i = 1) then

S_i \leftarrow S_i - 1;

// Fix incorrect blocks

if S_i = -1 then

S_i \leftarrow B^K - 1;

borrow \leftarrow 1;

// Propagate borrow

else

borrow \leftarrow 0;

return S;

```

#### 2.6.2 Multiplication

In 2000, the first attempted work [Coo00] using SIMD for accelerating large-number multiplication was done using SSE2 (128-bit vectorization) using a reduced-radix representation method, achieving a speedup of approximately 10.7x compared to a naive scalar implementation on an Intel Pentium 4 processor.

In 2012, a work [GK12] implemented a multiplication program using AVX2 and reduced-radix representation for modular arithmetic, which they patched into Open-SSL. Their evaluation showed a reduction of 50% in both the number of instructions and the number of cycles compared to the original OpenSSL. Furthermore, in 2016 they also investigated [GK16] the potential of AVX-512 instructions, including AVX-512IFMA and combinations of AVX-512F, AVX-512BW, and AVX-512VL. Their instruction count analysis for fixed operand sizes (1,024 to 4,096 bits) indicated that implementations using AVX-512F, VL, and BW had approximately half the number of instructions compared to the GMP, while AVX-512IFMA reduced the instruction count by approximately ranging between one-fourth to one-eighth relative to GMP. In 2014, this work [KM14] also implemented large integer multiplication using AVX-512 instructions with a 229-radix representation. Their evaluation was on an Intel Software Developer Emulator (SDE) simulating a Knights Landing processor, which showed a 1.16x reduction in the number of instructions compared to GMP for 2,048-bit multiplication. These prior works using the AVX2 or AVX512 family primarily evaluated their results based on instruction count and cycles due to the noncommercial availability of AVX in production. However, in 2018, the work [ET18]

utilizes AVX-512 intrinsics on an actual Intel Xeon Phi (Knights Landing) processor to accelerate large integer multiplication. For their implementation, they chose a *reduced-radix* representation (using 28 or 29 bits within 32-bit words) to manage carry propagation during the addition of partial products. To handle variable-length operands, they implemented a fixed-length base-case multiplication kernel(5) using grade-school multiplication(2.4.1) and repeatedly called it across the operands. Furthermore, they optimized the kernel by distributing sub-product arrays to minimize pipeline stalls caused by data dependencies, scenarios that might not be represented well through just instruction and cycle counts, as with prior works. The performance of their implementation was compared against the GMP, achieving execution times approximately 2.5x faster than GMP for operands of 1,024 bits to up to 7,168 bits. However, they have not provided their code of implementation, and we were unable to verify and compare their results on the latest CPUs.

#### Algorithm 5: Multiplication Kernel using AVX-512 [ET18]

```

Input: X = \sum_{k=0}^{m-1} x_k B^k, a multi-precision integer with m words in radix B = 2^N

(N=28 \text{ or } 29). Y = \sum_{k=0}^{n-1} y_k B^k, a multi-precision integer with n words in

Output: P = X \times Y = \sum_{k=0}^{m+n-1} p_k B^k, the product of A and B in radix B = 2^N.

// Vector Length for AVX-512

VLEN \leftarrow 8;

i \leftarrow 0;

while i < n do

i \leftarrow 0;

while j < m do

x \leftarrow [x_i, x_{i+1}, x_{i+2}, \dots, x_{j+(VLEN-1)}];

for k \leftarrow 0 to VLEN - 1 do

p \leftarrow [p_{j+k}, p_{j+k+1}, p_{j+k+2}, \dots, p_{j+k+(VLEN-1)}];

p \leftarrow p + x \times y_{i+k}; // Using AVX-512 intrinsics (_mm512_mul_epu32 and _mm512_add_epi64)

j \leftarrow j + VLEN;

i \leftarrow i + VLEN;

Convert P back to 2^N-radix representation;

return P;

```

In 2020, the work [ET20], by the same authors of [ET18], implemented large integer multiplication using Intel AVX-512IFMA intrinsics on a processor with Cannon Lake microarchitecture. They adopted a hybrid approach similar to GMP, vectorizing the base-case grade-school multiplication with AVX-512IFMA. The AVX-512F multiplication instructions discard the higher 64-bit of the resultant, requiring a 32bit or smaller data representation. In contrast, AVX512-IFMA multiplication instructions offer separate access to both the lower and upper 64-bit results, though they accept only 52-bit operands. Consequently, the authors used a reduced-radix representation with 52-bit words. They reported a speedup of up to 2.97x over GMP. In 2023, another study [ET23], by the same authors, employed a similar hybrid approach as [ET20], but this time using ARM-SVE for vectorization. Due to the absence of AVX512-IFMA-like 52-bit multiplication instructions for obtaining both higher and lower 64-bit results, the authors modified the base-case grade-school multiplication technique into what they called shifted grade-school multiplication 6. They achieved performance gains of up to 36% compared to GMP when using the trad mode of the fcc compiler and up to 31% when using the clang mode of the fcc compiler for operand sizes ranging from 3,072 bits to 14,336 bits. They also noted that the SVE implementation became faster than GMP for operands larger than 3,072 bits. However, for both works, we do not have access to their code and cannot verify and compare their results on the latest CPUs.

#### Algorithm 6: Shifted Basecase Multiplication Kernel [ET23]

```